# (12) United States Design Patent (10) Patent No.:

(45) **Date of Patent:** Hart

US D512,970 S

\*\* Dec. 20, 2005

## (54) UNIVERSAL LEAD STRAIGHTENER FOR INTEGRATED CIRCUIT DEVICES

(75) Inventor: Martin Hart, Irvine, CA (US)

Assignee: Topline Corporation, Garden Grove,

CA (US)

(\*\*) Term: 14 Years

(21) Appl. No.: 29/192,710

(22) Filed: Oct. 29, 2003

(51) LOC (6) Cl. ...... 13-03

(52) U.S. Cl. ..... D13/182

174/250, 260, 265; 140/105, 147; 29/407.1,

840

#### (56)References Cited

### U.S. PATENT DOCUMENTS

|     | 5,542,457 | Α          |   | 8/1996 | Gordon et al. |          |

|-----|-----------|------------|---|--------|---------------|----------|

|     | 5,640,308 | Α          | * | 6/1997 | Osann et al   | 361/777  |

|     | 6,014,993 | Α          | * | 1/2000 | Goins, III    | 140/105  |

|     | 6,026,566 | A          | * | 2/2000 | Urban et al   | . 29/840 |

|     | 6,740,822 | B2         | * | 5/2004 | Watanabe      | 174/260  |

| 200 | 3/0066681 | <b>A</b> 1 | * | 4/2003 | Uchida et al  | 174/260  |

|     |           |            |   |        |               |          |

# OTHER PUBLICATIONS

COOPER Tools, Weller WLSK1000 QFP Lead Repair Kit, CT97-0400/GP-92902/5M/Printed Jun. 1998/USA Cooper No. 55580-120-5 Copyright © 1998, Cooper Industries, Inc.

\* cited by examiner

Primary Examiner—Stella Reid Assistant Examiner—Selina Sikder

(74) Attorney, Agent, or Firm—Knobbe, Martens, Olson & Bear, LLP

#### (57)**CLAIM**

The ornamental design for a universal lead straightener for integrated circuit devices, as shown and described.

### DESCRIPTION

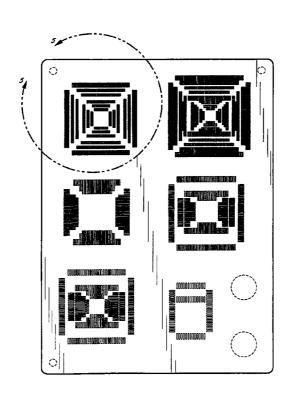

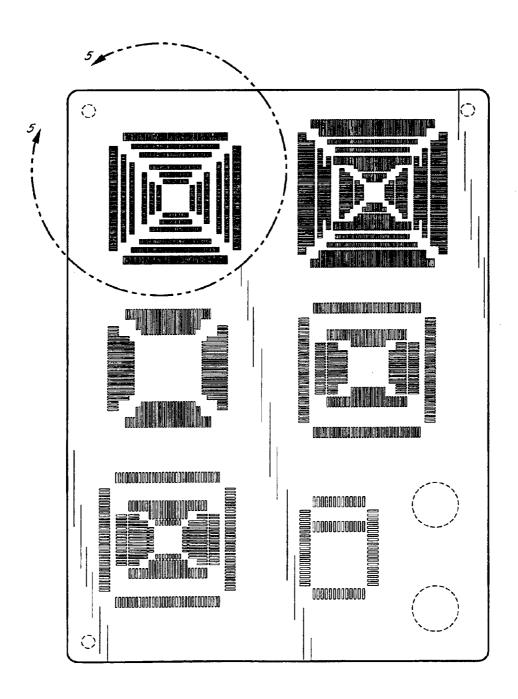

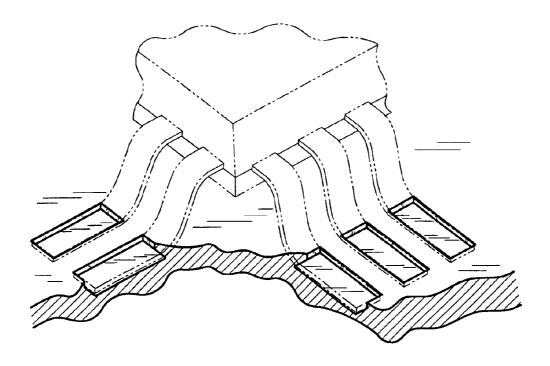

FIG. 1 is a front view of a universal lead straightener for integrated circuit devices showing the ornamental design. FIG. 2 is a back view thereof.

FIG. 3 is a left side view thereof, which is a mirror image of the right side.

FIG. 4 is a bottom edge view thereof which is a mirror image of a top edge.

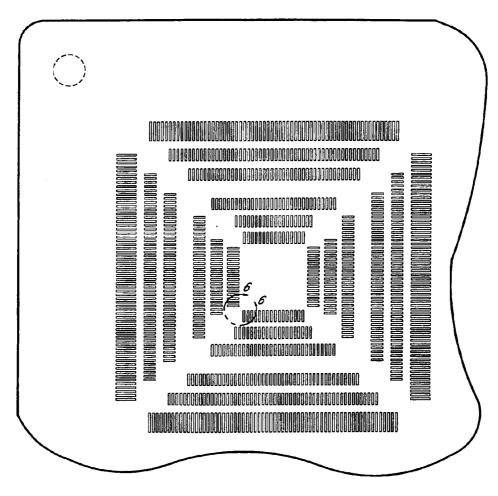

FIG. 5 is an enlarged view of a portion of FIG. 1, taken along the line 5-5 in FIG. 1; and,

FIG. 6 is a perspective, partially sectionalized view taken along the line 6-6 in FIG. 5 to illustrate the shallow recesses of the arrays and to illustrate in phantom lines the manner in which the leads of an integrated circuit device fit within the shallow recesses.

The broken line showing of the environment is for illustrative purposes only and forms no part of the claimed design.

# 1 Claim, 5 Drawing Sheets

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6